21 May 2014 (v3, 20 June 2014)

## The New CMS DAQ System for Run 2 of the LHC

Tomasz Bawej<sup>2)</sup>, Ulf Behrens<sup>1)</sup>, James Branson<sup>4)</sup>, Olivier Chaze<sup>2)</sup>, Sergio Cittolin<sup>4)</sup>, Georgiana-Lavinia Darlea<sup>6)</sup>, Christian Deldicque<sup>2)</sup>, Marc Dobson<sup>2)</sup>, Aymeric Dupont<sup>2)</sup>, Samim Erhan<sup>3)</sup>, Andrew Forrest<sup>2)</sup>, Dominique Gigi<sup>2)</sup>, Frank Glege<sup>2)</sup>, Guillelmo Gomez-Ceballos<sup>6)</sup>, Robert Gomez-Reino<sup>2)</sup>, Jeroen Hegeman<sup>2)</sup>, Andre Holzner<sup>4)</sup>, Lorenzo Masetti<sup>2)</sup>, Frans Meijers<sup>2)</sup>, Emilio Meschi<sup>2)</sup>, Remigius K. Mommsen<sup>5)</sup>, Srecko Morovic<sup>??,C)</sup>arlos Nunez-Barranco-Fernandez<sup>2)</sup>, Vivian O'Dell<sup>5)</sup>, Luciano Orsini<sup>2)</sup>, Christoph Paus<sup>6)</sup>, Andrea Petrucci<sup>2)</sup>, Marco Pieri<sup>4)</sup>, Attila Racz<sup>2)</sup>, Hannes Sakulin<sup>2)</sup>, Christoph Schwick<sup>2)</sup>, Benjamin Stieger<sup>2)</sup>, Konstanty Sumorok<sup>6)</sup>, Jan Veverka<sup>6)</sup>, Petr Zejdl<sup>2)</sup>

#### Abstract

The data acquisition system (DAQ) of the CMS experiment at the CERN Large Hadron Collider assembles events at a rate of 100 kHz, transporting event data at an aggregate throughput of 100 GB/s to the high level trigger (HLT) farm. The HLT farm selects interesting events for storage and offline analysis at a rate of around 1 kHz. The DAQ system has been redesigned during the accelerator shutdown in 2013/14. The motivation is twofold Firstly, the current compute nodes, networking, and storage infrastructure will have reached the end of their lifetime by the time the LHC restarts. Secondly, in order to handle higher LHC luminosities and event pileup, a number of sub-detectors will be upgraded, increasing the number of readout channels and replacing the off-detector readout electronics with a micro-TCA implementation. The new DAO architecture will take advantage of the latest developments in the computing industry. For data concentration, 10/40 Gb/s Ethernet technologies will be used, as well as an implementation of a reduced TCP/IP in FPGA for a reliable transport between custom electronics and commercial computing hardware. A 56 Gb/s Infiniband FDR CLOS network has been chosen for the event builder with a throughput of 4 Tbps. The HLT processing is entirely file based. This allows the DAQ and HLT systems to be independent, and to use the same framework for the HLT as for the offline processing. The fully built events are sent to the HLT with 1/10/40 Gb/s Ethernet via network file systems. Hierarchical collection of HLT accepted events and monitoring meta-data are stored into a global file system. This paper presents the requirements, technical choices, and performance of the new system.

<sup>4)</sup> University of California, San Diego, San Diego, California, USA

<sup>&</sup>lt;sup>1)</sup> DESY, Hamburg, Germany

<sup>&</sup>lt;sup>2)</sup> CERN, Geneva, Switzerland

<sup>&</sup>lt;sup>3)</sup> University of California, Los Angeles, Los Angeles, California, USA

<sup>&</sup>lt;sup>5)</sup> FNAL, Chicago, Illinois, USA

<sup>&</sup>lt;sup>6)</sup> Massachusetts Institute of Technology, Cambridge, Massachusetts, USA

Presented at RT2014 19th Real-Time Conference, IEEE Transactions on Nuclear Science, deadline 27th June 2014

# The New CMS DAQ System for Run-2 of the LHC

Tomasz Bawej, Ulf Behrens, James Branson, Olivier Chaze, Sergio Cittolin, Georgiana-Lavinia Darlea, Christian Deldicque, Marc Dobson, Aymeric Dupont, Samim Erhan, Andrew Forrest, Dominique Gigi, Frank Glege,

Guillelmo Gomez-Ceballos, Robert Gomez-Reino, Jeroen Hegeman, Andre Holzner, Lorenzo Masetti, Frans Meijers, Emilio Meschi, Remigius K. Mommsen, Srecko Morovic, Carlos Nunez-Barranco-Fernandez, Vivian O'Dell, Luciano Orsini, Christoph Paus, Andrea Petrucci, Marco Pieri, Attila Racz, Hannes Sakulin, *Member IEEE*, Christoph Schwick, Benjamin Stieger, Konstanty Sumorok, Jan Veverka and Petr Zejdl

Abstract-The data acquisition system (DAQ) of the CMS experiment at the CERN Large Hadron Collider assembles events at a rate of 100 kHz, transporting event data at an aggregate throughput of 100 GB/s to the high level trigger (HLT) farm. The HLT farm selects interesting events for storage and offline analysis at a rate of around 1 kHz. The DAQ system has been redesigned during the accelerator shutdown in 2013/14. The motivation is twofold: Firstly, the current compute nodes, networking, and storage infrastructure will have reached the end of their lifetime by the time the LHC restarts. Secondly, in order to handle higher LHC luminosities and event pileup, a number of sub-detectors will be upgraded, increasing the number of readout channels and replacing the off-detector readout electronics with a µTCA implementation. The new DAQ architecture will take advantage of the latest developments in the computing industry. For data concentration, 10/40 Gb/s Ethernet technologies will be used, as well as an implementation of a reduced TCP/IP in FPGA for a reliable transport between custom electronics and commercial computing hardware. A 56 Gb/s Infiniband FDR Clos network has been chosen for the event builder with a throughput of ~4 Tb/s. The HLT processing is entirely file based. This allows the DAQ and HLT systems to be independent, and to use the HLT software in the same way as for the offline processing. The fully built events are sent to the HLT with 1/10/40 Gb/s Ethernet via network file systems. Hierarchical collection of HLT accepted events and monitoring meta-data are stored into a global file system. This paper presents the requirements, technical choices, and performance of the new system.

#### I. INTRODUCTION

THE Compact Muon Solenoid (CMS) experiment [1, 2] at CERN's Large Hadron collider is one of two large general-purpose experiments exploring a wide range of physics at the TeV scale. Its on-line systems need to select around 1 kHz of interesting events out of the LHC bunch-

U. Behrens is with DESY, Hamburg, Germany.

J. Branson, S. Cittolin, A. Holzner and M. Pieri are with University of California San Diego, La Jolla, California, USA.

G. Darlea, G. Gomez-Ceballos, C. Paus, K. Sumorok and J. Veverka are with Massachusetts Institute of Technology, Cambridge, Massachusetts, USA.

crossing rate of nominally 40 MHz. At CMS, the event selection is done with only two trigger levels: a first-level trigger [3], based on custom electronics, reduces the rate to 100 kHz. The data acquisition (DAQ) system [4] then reads out the detector and assembles full events at 100 kHz, passing the assembled events to the high-level trigger, a software system based on the full CMS reconstruction software, running on a farm of computers. At a nominal event size of 1 MB, the CMS DAQ system for Run-1 was designed to handle a throughput of 100 GB/s, making it the highest throughput DAQ system in high-energy physics to date. The DAQ system has performed very successfully during Run-1 of the LHC from 2009 to 2013, acquiring physics data with an availability of 99.6 % [5].

During its current first long shut down, the LHC is being upgraded to provide higher center-of-mass energy and higher luminosity from 2015 onwards. CMS therefore needs to prepare for higher pile-up and thus higher event size. Some of the CMS sub-systems are currently upgrading their detectors and/or on-line systems and are building new off-detector readout electronics based on the µTCA standard. The DAQ system for Run-2 will need to be able to read out these new offdetector electronics though a new optical readout-link at a higher bandwidth than in Run-1. Since many of the compute nodes and part of the networking infrastructure of the DAO system for Run-1 are close to the end of their life cycle, we decided to completely re-design the DAQ system exploiting the considerable advances in computing and network technology to build a much more compact and even more powerful DAQ system. In this paper we present the final design of the new DAQ system that is currently being installed, and report on performance measurements including first measurements in the production system.

In Section II we give an overview of the main design parameters of the new CMS DAQ system. In sections III, IV, V and IV, we then report in more detail on the new frontendreadout optical link including a 10 Gb/s TCP/IP sender implemented in an FPGA and the new SLINK-Express DAQ readout link, the new data concentrator network based on 10/40 Gb/s Ethernet, the new core event builder based on Infiniband and our new file-based way of integrating the highlevel trigger. In each of the sections we report on the requirements, design and on latest performance measurements.

Manuscript received May 21, 2014. This work was supported in part by the DOE and NSF (USA).

T. Bawej, O. Chaze, C. Deldicque, M. Dobson, A. Dupont, A. Forrest, D. Gigi, F. Glege, R. Gomez-Reino, J. Hegeman, L. Masetti, F. Meijers, E. Meschi, S. Morovic, C. Nunez-Barranco-Fernandez, L. Orsini, A. Petrucci, A. Racz, H. Sakulin (corresponding author. phone: +41 22 767 3506, fax: +41 22 767 8940, e-mail: Hannes.Sakulin@cern.ch), C. Schwick, B. Stieger and P. Zejdl are with CERN, Geneva, Switzerland.

S. Erhan is with University of California, Los Angeles, California, USA.

R. K. Mommsen and V. O'Dell are with FNAL, Batavia, Illinois, USA.

#### II. MAIN DESIGN PARAMETERS

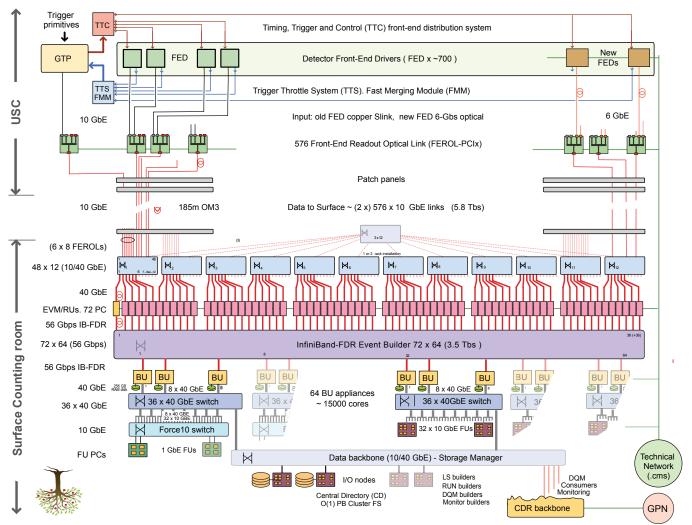

Table 1 compares the main design parameters of the CMS DAQ system for Run-1 (DAQ-1) and of the new CMS DAQ system for Run-2 (DAQ-2). The readout rate will remain at 100 kHz as it is limited by on-detector electronics of several CMS sub-systems. In order to cater for higher event sizes, fragments of up to 4 kB will be supported for legacy readout electronics based on SLINK-64 [6]. For new readout electronics based on uTCA, the new readout-link standard SLINK-express will be supported with fragment sizes up to 8 kB. The total bandwidth of the DAQ system will be doubled to 200 GB/s, allowing for event sizes up to 2 MB, which includes a large margin. As in Run-1, the new DAQ-2 system will build events in two stages (see Fig. 1). But unlike in Run-1, where a cost-effective switch with the required capacity was not available, advances in network technology made it possible to implement the stage-2 (core) event builder with a single network. The first stage of the DAQ-2 event builder is thus a pure data concentrator. The development of a custom 10 Gb/s network card sending TCP/IP from an FPGA made it possible to interface the custom electronics of the DAO readout link to a commercial 10/40 Gb/s Ethernet network handling the data concentration. The high throughput of the

event builder makes it impractical to combine Builder Units (BU) and Filter Units (FU) on the same machines as done in Run-1. In Run-2, the high-level trigger will therefore run on dedicated FU machines connected to the BUs via 1/10/40 Gb/s Ethernet.

TABLE 1 MAIN PARAMETERS OF THE CURRENT (DAQ-1) AND RUN-2 (DAQ-2)

| CMS DAQ SYSTEMS.        |                       |                      |

|-------------------------|-----------------------|----------------------|

|                         | DAQ-1                 | DAQ-2                |

| Readout rate            | 100                   | kHz                  |

| Front-End-Drivers,      | 640: SLINK-64         | 640: SLINK-64,       |

| type of readout link,   | 1-2  kB               | 1 - 4  kB            |

| fragment size           |                       | 50: SLINK-Express    |

| -                       |                       | 2-8 kB               |

| Total DAQ bandwidth     | 100 GB/s              | 200 GB/s             |

| Event Builder Stage 1   | 2x 2.5 Gb/s Myrinet   | 10/40 Gb/s Ethernet  |

| Data concentration      | (commercial hardware, | (custom sender card, |

|                         | custom firmware &     | commercial TCP/IP    |

|                         | protocol)             | protocol)            |

| Number & type of        | 640 (8 x 80)          | 84                   |

| readout-unit PCs        |                       |                      |

| Event Builder           | 1x/2x/3x 1 Gb/s       | 56 Gb/s FDR          |

| Network                 | Ethernet              | Infiniband           |

| Number of parallel      | 8                     | 1                    |

| event builders (slices) |                       |                      |

| Event Builder           | 1 switch per slice    | 1 Clos network of 18 |

| topology                |                       | switches             |

Fig. 1. Over-all architecture of the new CMS DAQ system for Run-2 of the LHC. See text.

| Number of Builder    | 1260 (8 x 158)          | 64, builder only      |

|----------------------|-------------------------|-----------------------|

| PCs                  | builder + filter in one |                       |

| Number of HLT cores  | 13000                   | ~15000 initially      |

| Interface to the HLT | Shared memory           | Files                 |

| Storage              | 16 SAN systems          | 1 cluster file system |

| Bandwidth to storage | 1.2 GB/s write          | 2 GB/s write          |

| -                    | + 1 GB/s read           | + 1 GB/s read         |

| Storage capacity     | ~ 250 TB                |                       |

## III. THE NEW FRONT-END-READOUT OPTICAL LINK

During Run-1, CMS sub-detectors were read out exclusively through the SLINK-64 DAQ readout link, an LVDS-based copper link capable of transferring up to 400 MB/s. One or two such links are received by the Frontend Readout Link (FRL), a custom Compact-PCI card, which forwarded the data to a commercial Myrinet NIC via an internal PCI-x bus. Super-fragments were then assembled using a commercial Myrinet network running custom firmware on the NICs to do the super-fragment building. Assembled superfragments were then transferred into the memory of a Readout Unit (RU) PC via DMA.

In the Run-2 DAQ-system, the Myrinet NIC on the FRL is replaced by a newly developed custom PCI-x card, the Frontend Readout Optical Link (FEROL) [7]. The FEROL acts as a 10 Gb/s Ethernet NIC sending data to the event builder. It receives data either via the PCI-X interface from the FRL (from the bulk of the sub-systems that continue to use SLINK-64) or via new optical SLINK-express inputs from new or upgraded sub-systems. Up to two SLINK-express inputs at 6 Gb/s or one input at 10 Gb/s will be supported. While SLINK-64 senders are mezzanine cards plugged onto the off-detector readout electronics, SLINK-express senders are firmware IP-cores distributed to the sub-systems. (Many sub-systems use the AMC-13 [8] card, which includes this IP core.) SLINK-express works with 8b/10b encoding at up to 6.3Gb/s or 64b/66b encoding at 10.3 Gb/s resulting in an effective bandwidth of up to 5.0 Gb/s or 10.0 Gb/s, respectively. The data format will be identical to that of SLINK-64. SLINK-express works with a 4kB packet size and supports retransmission.

At the output side, the FEROL sends data via TCP/IP directly from FPGA firmware, without the need of a software stack. This has been achieved though a simplification of the TCP/IP protocol for unidirectional use, which reduces the number of states from 11 to 3 [9]. TCP/IP streams (one per input) are sent via a commercial 10/40 Gb/s Ethernet switch to a commercial 40 Gb/s Ethernet NIC in the Readout Unit (RU) PC where they can be received with the standard Linux TCP/IP stack. In a test setup sending data from a single FEROL through a switch to a receiving PC running Linux sockets with some performance tuning, a sustained point-to-point throughput of 9.7 Gb/s was shown to be achievable for fragments larger than 1 kB [7].

#### IV. DATA CONCENTRATION

As shown in Fig. 1, the data concentration layer consists of individual 10/40 Gb/s Ethernet switches (Mellanox

MSX1024) receiving data at 10 Gb/s from up to 48 FEROLs each, sending the data at 40 Gb/s to up to 6 Readout Unit PCs. Readout links from legacy off-detector electronics will be typically merged by 12, allowing for up to 4 kB fragment size, while readout links from upgraded detectors will be merged less aggressively, allowing for larger fragment sizes up to 8 kB. In order to increase tolerance to failures of readout unit PCs, the switches will be interconnected with a small number of additional switches in a fat tree [10] topology so that data may also be sent to a Readout Unit on a neighboring switch.

As RU PCs we are using the Dell PowerEdge R620 machines with dual 12-core E5-2670 CPUs and dual Mellanox ConnectX-3 NICs (one configured for Ethernet, one for Infiniband). The software receiving TCP streams from the FEROLs is based on Linux sockets. In order to achieve full throughput at 40 Gb/s, two threads are used for receiving data. CPU affinities of threads, interrupts and memory are fine-tuned manually [11].

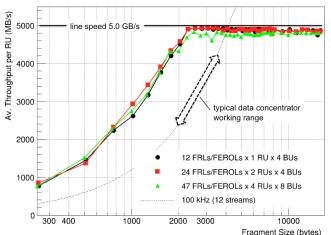

Fig. 2 shows a measurement of the throughput of the RU as a function of the fragment size for fixed size fragments when merging fragments from 12 FEROLs sending 1 stream each. Setups with 1, 2 or 4 RUs, all connected to the same 10/40 Gb/s Ethernet switch, were tested, showing that the performance does not significantly degrade when using all inputs of the switch. The setups also included the full core event builder (see Section IV) with 4, 4 and 8 Builder Units, respectively. However, the core event builder has no influence on this measurement at fragment sizes up to 2 kB, and only a small influence above. In this measurement, FEROLs were sending fragments as fast as possible. Up to about 2 kB fragment size, the observed throughput is limited by the overhead of TCP/IP in the data concentrator, while at higher fragment sizes almost the full capacity of the 40 Gb/s link is used. The required rate of 100 kHz can be achieved for fragment sizes of up to 3.5 kB when merging from 12 sources (using 90% of the bandwidth). In the presented measurement, Ethernet pause frames are the main mechanism for flow control. Alternatively, FEROLs also support congestion control by means of a local TCP congestion window.

Fig. 2. Throughput per Readout Unit as a function of fragment size for fixed size fragments in saturation mode.

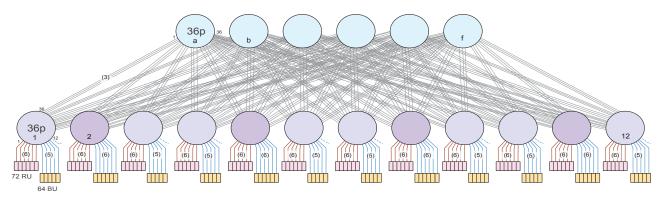

Fig. 3. Infiniband Clos network composed of 12 leaf and 6 spine switches with 36 ports each.

## V. THE CORE EVENT BUILDER

The core event builder of the new DAQ system is based on 56 Gb/s FDR Infiniband. Infiniband is a high-speed, lowlatency interconnect used in data centers. It is currently the most popular interconnect in the top-500 supercomputers. Infiniband supports credit-based flow control, which enables it to efficiently avoid congestion without the need for large buffer memories in the switches. This feature also allows us to construct a large network in a cost effective way by combining small switches.

The core event builder of the DAQ-2 system consists of 84 Readout Units by 64 Builder Units. The switching fabric is composed of 18 individual 36-port switches, 12 used a leaves and 6 used as spine arranged in a Clos network as shown in Fig. 3. The switching fabric has a total bandwidth of 6 Tb/s per direction out of which we are using 4 Tb/s on the RU side and 3.5 Tb/s on the BU side. Leaf switches will be shared between RUs and BUs allowing for more effective use of the leaf-to-spine connections. With 216 external ports, the switch fabric leaves room for future extensions of the event builder, should requirements change. As BUs we are using Dell PowerEdge R720 machines, equipped with the same CPUs and NICs as the RUs but with additional RAM (see section VI). Our online-software is based on the Verbs API [12]. Data are transferred by DMA avoiding the need for copies. CPU affinities are fine-tuned manually for threads, interrupts and memory. While the event builder software for Run-1 was mostly single-threaded, we now use 4 threads on the RUs to pack data and 6 threads on the BUs to assemble and write data.

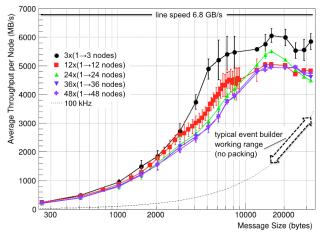

Very first measurements with a part of the installed network (up to 48 RUs by 48 BUs) show that for the typical expected super-fragment size of 16 to 32 kB, a per-node throughput above 4 GB/s can be achieved (Fig. 4). These measurements show the simultaneous sending and reception of streams without any event building at this stage. These measurements make us confident that the nominal overall event builder throughput of 200 GB/s can be easily achieved with this network.

## VI. FILE-BASED FILTER FARM (F3)

The CMS High-Level Trigger (HLT) performs online event selection using the full reconstruction framework CMSSW [13], which is primarily geared to off-line use, typically reading input data from files. For on-line use in Run-1, the event selection code has been integrated into an onlinesoftware application based on the XDAQ framework [14], which is responsible for data transport in the DAQ system. The two software frameworks therefore needed to be tightly coupled, forcing us to use the same compiler version and externals and to align our release schedules. This tight coupling also made debugging more complex, as in many cases knowledge about both frameworks was required.

For Run-2 we are aiming at completely separating the two frameworks [15]. Builder Units PCs will write the assembled events to a local RAM-disk. The event-selection code will run on Filter Unit (FU) PCs connected to the BU PCs via a 1/10/40 Gb/s Ethernet network as shown in Figure 1. FUs will be statically assigned to a certain BU, the ensemble of a BU and its FUs being called an appliance. FUs will mount the RAM disk of their BU via a network file system, so that

Fig. 4. Throughput per node on the Infiniband Clos network as a function of the message size for fixed size messages. Data are simultaneously streamed from n sources to n destinations with sources and destinations residing on separate leaf switches. No event building is performed.

CMSSW processes can run exactly as in off-line mode, reading input data from files. A RAM disk size of 256 GB per BU, corresponding to about 2 minutes of data, will allow us to decouple the event builder from the high-level trigger so that back-pressure can be avoided, especially during start-up of the HLT. With the current single-threaded version of CMSSW, we will start two processes per core (one per hyper-thread) to fully load the machines, as done in Run-1. A multi-threaded version of CMSSW and the corresponding HLT modules are being developed which will allow us to fully load the machines with fewer processes.

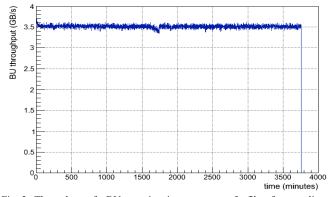

Fig. 5 shows a measurement of the BU throughput in a test setup in which 4 RUs are sending data to an appliance consisting of 1 BU and 8 FUs, the latter running 32 CMSSW processes each. BUs are writing all data to RAM disk. FUs have the RAM disk mounted via NFS-4 and are reading concurrently. A constant throughout of 3.5 GB/s was measured for one appliance, which will allow us to achieve over 200 GB/s with 64 appliances.

Fig. 5. Throughput of a BU over time in a test setup of a filter farm appliance.

The filter farm will initially be made up of three generations of machines: the Westmere and Sandy Bridge based Dell PowerEdge C6100 and C6220 machines that were purchased in 2011 and 2012 and a new type of machine to be purchased in 2015. For the first two generations, two links at 1 Gb/s link will be sufficient to feed the FU. We will re-use the Force-10 1/10 Gb/s Ethernet switches used in the Run-1 event builder to connect these two generations of machines to the main 10/40 Gb/s switches. The third generation of machines will be directly connected with a 10 Gb/s link.

## VII. DATA COLLECTION AND STORAGE

The CMSSW processes will write their output files to the local hard disk of the FU, producing one file per process and per HLT stream (typically around 10 streams are used) in each luminosity section – a period of 23 s that is used as the quantum for data certification. These files will then be merged in two stages: The first merging stage will merge the output files from all processes running on a FU and copy them back to a hard disk on the BU. On the BU, the second merger stage will merge the output files of all FUs in the appliance and write the results to a storage system running a cluster file system. We are planning to use Lustre [16] as a cluster file system. With Lustre it will be possible to perform the final

merge by simultaneously writing data to the same file from all BUs, so that the storage system will only need to sustain the write throughput of 2 GB/s from 64 BU nodes and a simultaneous read throughput of 1 GB/s for transfers to the CERN computing center. Measurements on an evaluation system at NetApp comprising 15 clients and 4 Object Storage Servers running Lustre 2.4 show that this technology can meet our requirements. The data collection and storage system will also collect and merge special streams and histograms for data quality monitoring.

#### VIII. STATUS AND OUTLOOK

The DAQ system of the CMS experiment has been redesigned during the ongoing first long shutdown of the LHC. By relying on modern networking technologies such as 10/40 Gb/s Ethernet and 56 Gb/s FDR Infiniband, the event builder now comprises an order of magnitude fewer machines with respect to the previous DAQ system, while its bandwidth was doubled to 200 GB/s. Installation of the event builder is complete and all front-end readout links have been switched over to the new event builder. First performance measurements of individual parts of the system indicate that the nominal performance can be achieved or even exceeded. The system will be commissioned and completed with a new generation of Filter Units over the remainder of 2014 and early 2015.

#### REFERENCES

- The CMS Collaboration, CMS Technical Proposal, CERN LHCC 94-38, 1994.

- [2] The CMS Collaboration (R. Adolphi et al.), "The CMS Experiment at CERN LHC", JINST 3 S08004 p. 361, 2008.

- [3] The CMS Collaboration, The TriDAS Project, Technical Design Report, Volume 1: The Trigger Systems, CERN/LHCC 2000-38, 2000.

- [4] The CMS Collaboration, The TriDAS Project, Technical Design Report, Volume 2: Data Acquisition and High-Level Trigger, CERN/LHCC 2002-26, 2002.

- [5] G. Bauer et al., "Automating the CMS DAQ", presented at CHEP 2013, Amsterdam, submitted to J. Phys.: Conf. Ser., 2013

- [6] A. Racz, R. McLaren, E. van der Bij, The S-Link 64 bit Extension Specification: S-Link64, http://hsi.web.cern.ch/HSI/s-linkSLINK64

- [7] G. Bauer et al., "10 Gbps TCP/IP streams from the FPGA for the CMS DAQ Event Builder Network", JINST 8 C12039 doi:10.1088/1748-0221/8/12/C12039, 2013

- [8] E Hazen et al., "The AMC13XG: a new generation clock/timing/DAQ module for CMS MicroTCA", JINST 8 C12036 doi:10.1088/1748-0221/8/12/C12036, 2013

- [9] G. Bauer et al., "10 Gbps TCP/IP streams from the FPGA for High Energy Physics", presented at CHEP 2013, Amsterdam, submitted to J. Phys.: Conf. Ser.

- [10] C. E. Leiserson, "Fat-trees: universal networks for hardware-efficient supercomputing", IEEE Transactions on Computers, Vol. 34, no. 10, Oct. 1985, pp. 892-901.

- [11] T. Bawej et al., "Achieving High Performance with TCP over 40GbE on NUMA architectures for CMS Data Acquisition", in these proceedings

- [12] T. Bawej et al., "Boosting Event Building Performance using Infiniband FDR for CMS Upgrade", to be presented at TIPP, Amsterdam, June 2014.

- [13] C. D. Jones et al., "The new CMS data model and framework", CHEP'06 Conference Proceedings, 2007

- [14] G. Bauer et al., "The CMS data acquisition system software", J. Phys.: Conf. Ser. 219 022011, 2010

- [15] Bauer G et al., "Prototype of a File-Based High-Level Trigger in CMS", presented at CHEP 2013, Amsterdam, submitted to J. Phys.: Conf. Ser.

- [16] Lustre. www.lustre.org