# Computing challenges in the certification of ATLAS

MobiDICK

Tile Calorimeter front-end electronics during maintenance periods

C. Solans<sup>1</sup>, F. Carrió<sup>2</sup>, H.Y. Kim<sup>3</sup>, P. Moreno<sup>4</sup>, R. Reed<sup>4</sup>, C. Sandrock<sup>4</sup>, X. Ruan<sup>4</sup>, A. Shalyugin<sup>5</sup>, V. Schettino<sup>6</sup>, J. Souza<sup>6</sup>, G.Usai<sup>3</sup>, A. Valero<sup>2</sup> On behalf of the ATLAS Tile Calorimeter System

1. CERN, 2. IFIC-UV (Spain), 3. UTA (USA), 4. Univ. of Witwatersrand (South Africa), 5. JINR (Russian Federation), 6. UFJF (Brazil)

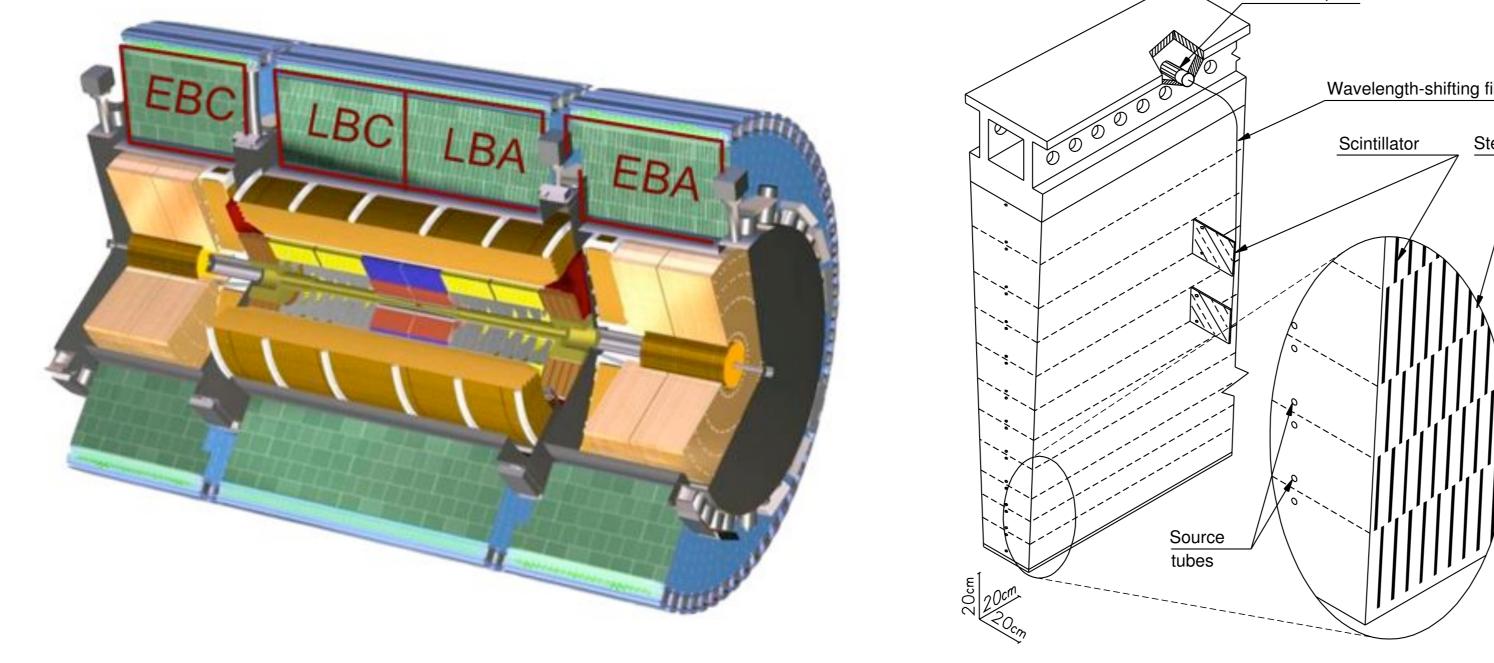

### **The ATLAS Tile Calorimeter**

The hadronic Tile Calorimeter is a sampling calorimeter where iron plates are embedded with plastic scintillating tiles. It covers the pseudo-rapidity region of -1.7 to 1.7, and is split into three barrels, two extended and one central long barrel instrumented on both sides. Each barrel is azimuthally divided into 64 wedges and radially segmented in three layers. The light produced in the tiles is guided on each side of the module to the outer most part region, where the front-end electronics is located. Groups of tiles that define calorimetric cells are read-out by a single PMT.

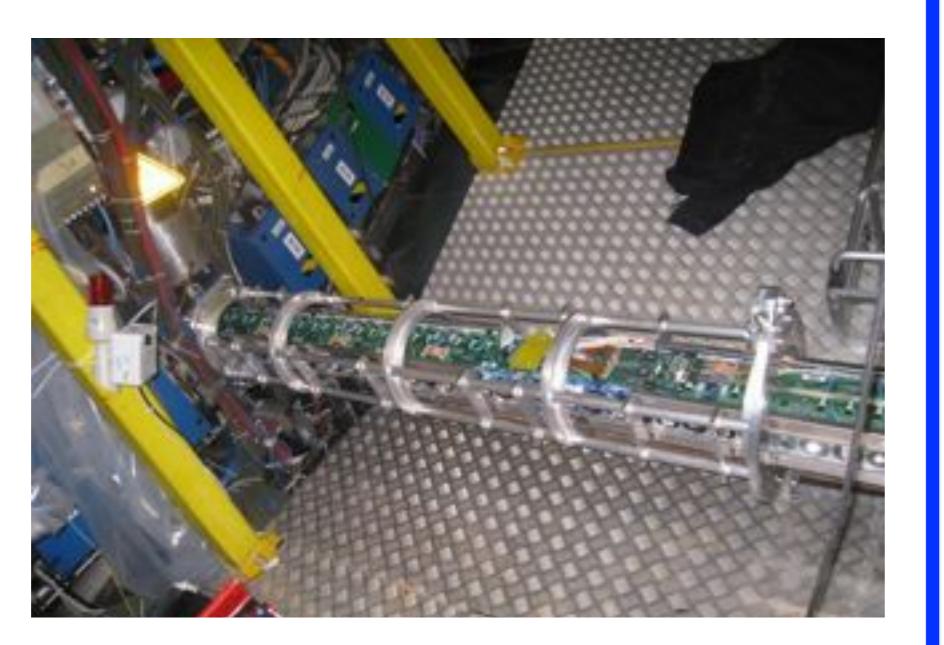

#### The Mobile Data Integrity Check (MobiDICK) system was recently upgraded to replace the ten year old VME based version in order to extend its lifetime and support. The new generation of MobiDICK increases the portability and reliability, provides a quicker turn around and improves the

### Maintenance periods

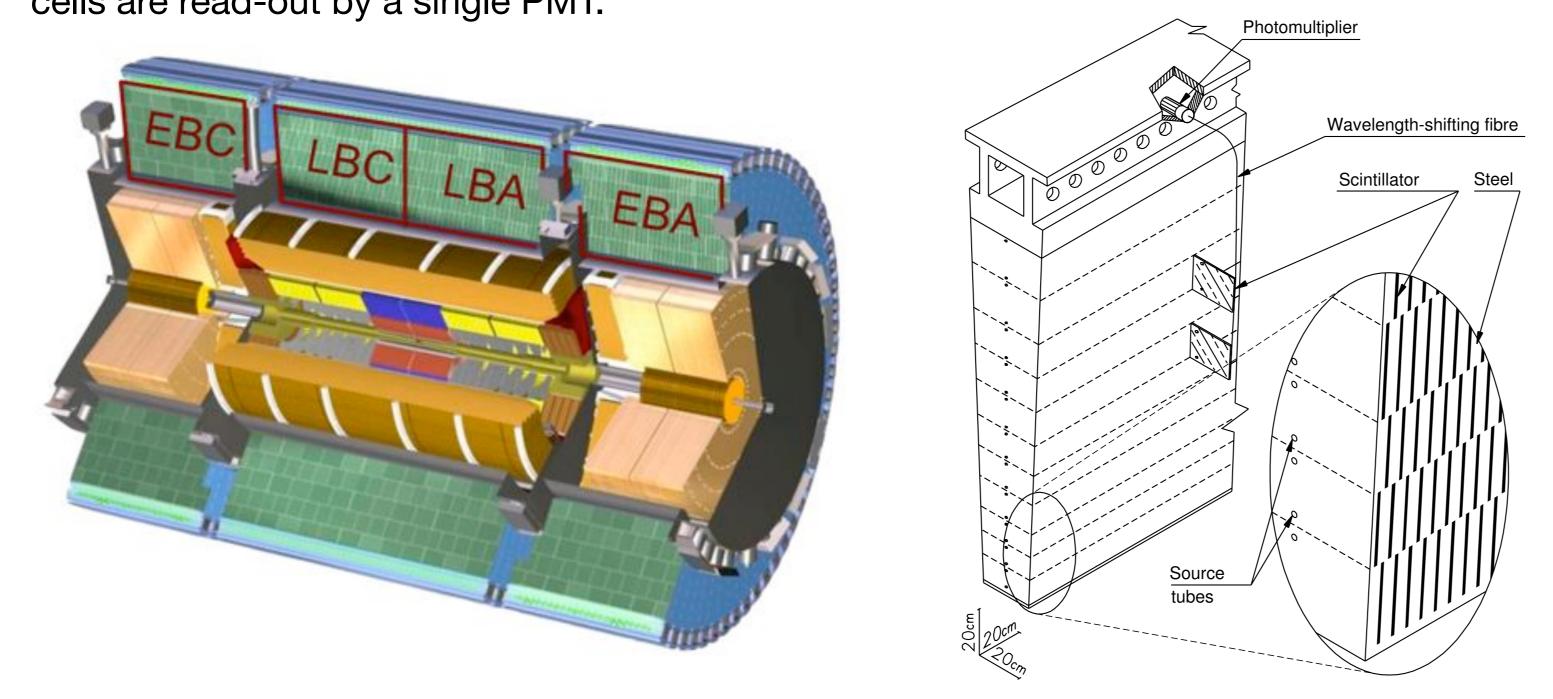

During the long shutdown of the LHC, the Tile front-end electronics are extracted for consolidation work for operating at design specifications. All the functionalities of electronics are checked. Any under performing component is replaced and complementary reinforcements are made on connectors. The certification is assessed once before the repairs but after extraction and another time once the super-drawer is back into its final position. All 256 modules need to be extracted and checked.

overall test-bench experience.

### **Embedded design**

MobiDICK is based on an FPGA embedded system core which controls different commercial devices or custom components that provide the functionalities required to communicate with the system.

ADC board digitizes the analog trigger outputs, SFP module connects to

Completely encapsulated inside a box that is not dependent from external resources, MobiDICK is the perfect tool for electronics certification.

## **Computing challenges**

Requirements for the test-bench were re-evaluated leading to a completely new re-design of the system. The new generation MobiDICK has better performance in half of the volume and almost a tenth of the weight.

### **Dependable evolution**

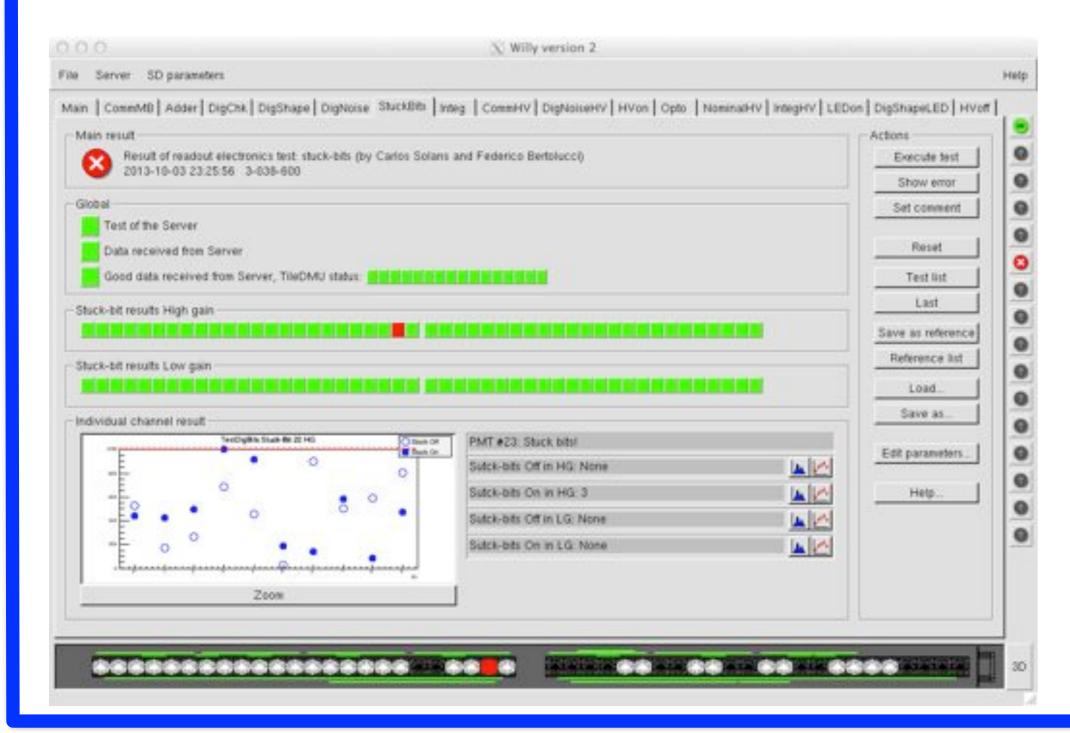

MobiDICK provides new functionalities in addition to enhanced and reliable measurements while meeting the initial requirements. A new test was provided to detect stuck bits in the samples originated in the front-end digitizer boards. A set of pulses that vary amplitude, phase and pedestal are used to scan over all possible values of the 10-bit ADC and errors show up in the GUI.

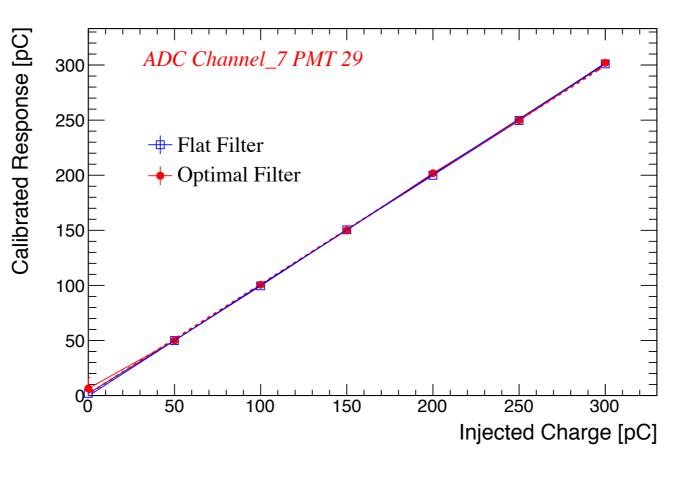

Software has been recycled as much as possible and simplicity favoured in the design. A flat filtering method based on the sum of samples is used to reconstruct the injected charge in MobiDICK. Results are compatible with those made with other sophisticated algorithms like optimal filtering which was disfavoured. The GUI was made compatible with other Unix-like environments like OSX. Limitations of the CAN bus speed of the new system have been overcome by reducing the number of points used by the tests, without affecting the results.

the TTC and GLink optical links, LED driver illuminates the PMTs with a known pulse of amplitude and time, HV board provides HV for PMT operation, and CAN bus dongles interface with Integrator and HV systems.

### **Real-time processing**

The motherboard provides all the computing power required by the system in a synergy between VHDL modules and C++ algorithms. Due to the system's flexibility to implement real-time processing tasks, it has been possible to deploy the test to check for format and CRC errors in all data fragments at the nominal Level 1 Trigger rate (100 kHz). A VHDL module checks every event, while C++ reads the error counters available and the user is updated at a rate that he considers real-time. C++ code is used at lower rates and when more complex algorithms are required for every event.

#### **Precision measurements**

Reference: NIM A518, 509-510 (2004)

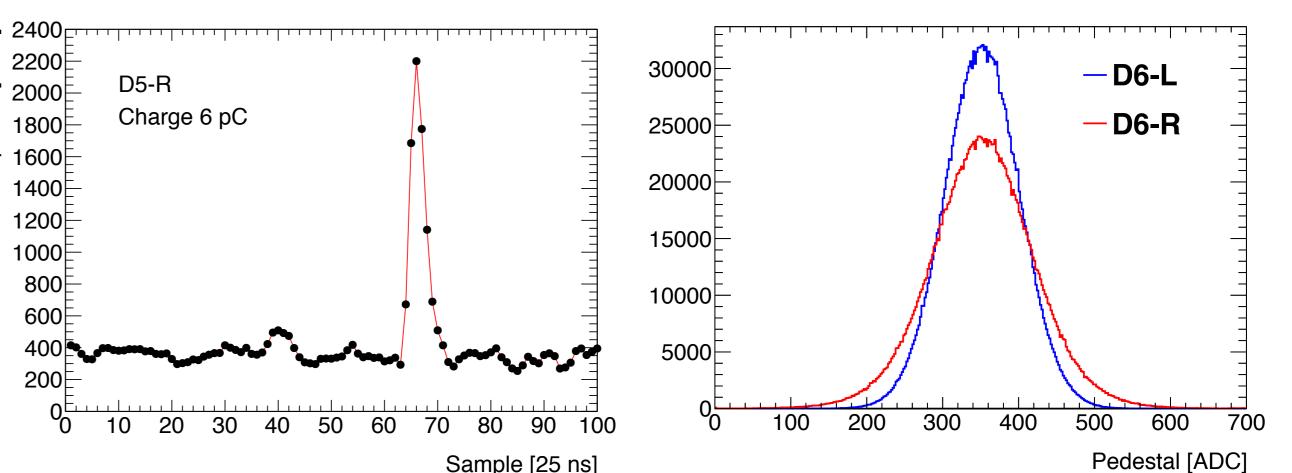

#### Sample [25 ns]

Analog trigger outputs of the super-drawer can be monitored with the system acting as a digital scope. Up to 128 samples can be stored at a time obtained with a sampling rate of 40 Msps. Recent measurements show different noise distribution for the PMTs in D6 cells.

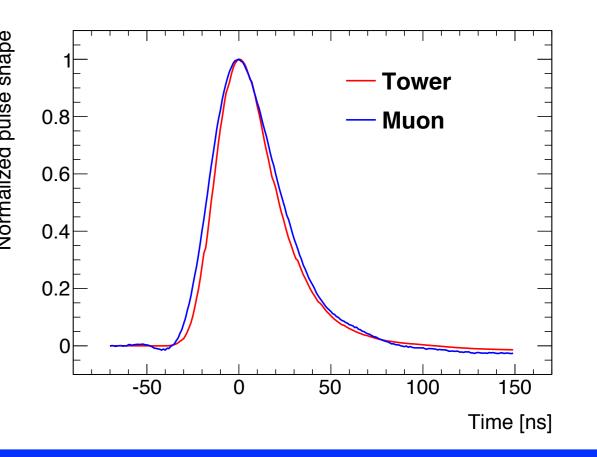

Precise pulse shape measurement of the tower and muon outputs of the super-drawer were obtained by the ADC board by sampling a signal at different injection phases. As expected, muon output has slightly wider distribution, compatible with previous measurements.

20th International Conference on Computing in High Energy and Nuclear Physics 2013 – Amsterdam, Netherlands